It's the network, stupid

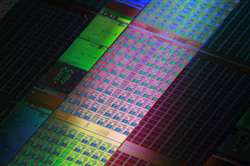

I recently had a chance to talk with Thom Sawicki, technology strategist for the Intel Communications Technology Lab, about the company's ongoing 80-core "Terascale computing" research initiative. Sawicki brought me up to speed on where Intel is headed with the project, and gave some hints as to the kinds of announcements we can expect to see from the company in the coming year.

Since this wasn't a formal interview, I won't reproduce the chat Q&A-style. Instead, I'll summarize what Intel is up to and how the company hopes that the Terascale project will contribute to the next few stages in multicore evolution. Then I'll give some of my own concluding thoughts on the project.

Terascale not about building a DSP toaster

The focus of my chat with Sawicki was to look beyond the recent 80-core announcement and specifically beyond the simple fact that someone has put 80 cores on a single chip and called it a "processor." The idea was to talk about the larger implications of massively multicore processor for system- and network-level architecture.

The focus of my chat with Sawicki was to look beyond the recent 80-core announcement and specifically beyond the simple fact that someone has put 80 cores on a single chip and called it a "processor." The idea was to talk about the larger implications of massively multicore processor for system- and network-level architecture.

"Once you jump to terascale, you have to ask and need to ask 'what are the implications for everything?'" said Sawicki. "The platform of the future when you get to terascale will look different and act different. It won't be a CPU of 80 cores surrounded by a chipset and some peripheral. You'll see a much tighter, more integrated organization."

So things that people take for granted, like the basic divide between processing hardware and off-chip I/O hardware, are being questioned as part of the project. Indeed, a big part of the project at this early stage seems to be to provide a venue for asking anew a slew of fundamental questions about system- and network-level architecture, and in looking for answers based on the new assumption that you can put a 80 cores worth of useful hardware on a single chip.

The "useful" part of this is key, because to focus on the fact that the current 80-core prototype consists of fairly lightweight floating-point-only cores misses the point. Contrary to popular belief, the goal of Terascale isn't to make a DSP toaster, but rather to figure out the hows and whys of putting 80 of any kind of core on a single processor. Sawicki emphasized that the kind of 80-core chip that Intel envisions one day bringing to market would consist at least partially of more general-purpose cores, each of which is capable of serving data onto the network.

A server room on a chip

"When you start looking at these large numbers of cores, you start thinking about how are you going to use them," Sawicki told me. This usage question goes beyond the problem of writing massively parallel programs for an 80-core chip, and Intel's quest for the answer has brought them into the realm of network architecture.

The picture that Sawicki painted is of a server-room-on-a-chip—a single piece of silicon that uses many cores and virtualization to do the kind of work that it currently takes multiple networked servers to do. Sawicki gave the example of a hypothetical multicore chip that can run a high-volume e-commerce solution on a single piece of silicon. Instead of web server box that takes orders and then sends them over the network to another machine for processing, you could use two separate cores for these tasks, with each core running a virtual server.

Problems might arise, however, when an order comes in through the virtual web server, and then order data has to be moved to another virtual server for processing. Ideally, you want the transaction data to move from virtual server to virtual server—and from core to core—without leaving the chip, Sawicki explained. It would be a waste to send those packets off the chip to a router to reach a destination that's a few cores away.

Sawicki said that part of the challenge that Intel sees with massively multicore computing lies in how to handle the IP network stack. If each core were to have its own IP address, then you wouldn't necessarily want all those cores to go through the entire network stack every time they want to talk to each other.

"Would it make sense to take a NIC/MAC-type functionality, where for an 80-core chip ten of those are an integrated NIC/MAC function, or am I better off trying to infuse some of the network functions and logic into each core?" asked Sawicki. "Where is the proper and best breakdown of what gets done today in a peripheral device vs. what part of the stack gets done in the CPU?"

"We get to play with all these [options]," he said, "and that's the work under way in the lab. We'll start seeing over time what the answers are."

Other network architecture questions that Intel is asking concern security. "Is security necessary for just the packets coming into the system, or do we need security between the cores as well?" Sawicki asked. "These are things we've got to start working on now, and that's the research that's underway."

reader comments

0